*출처 및 참고문헌: 월간 전자부품 *출처 및 참고문헌: 월간 전자부품

반도체 제조공정 기술의 발달로 집적도가 향상됨에 따라서 하나의 시스템을 이루는 프로세서,

메모리, 주변장치(Peripheral), 그리고 주변 로직들이 원 칩으로 구현 가능한 시대가 열렸다.

가장 유력한 솔루션이라 할 수 있는 ASIC의 경우, 시스템 전체가 집적화 됨으로써 설계부터

시작하여 그 이후 테스트 단계에 이르기까지 검증해야 할 시간 및 양적인 부분 또한 함께

증가되므로 개발기간의 장기화와 비용증가를 피할 수 없다. 이러한 틈새를 노린 프로그래머블

로직 업체들의 행보가 주목된다.

주요 PLD 벤더들은 자사의 디바이스에 프로세서 코어를 임베디드하여 사용자가 직접 SoC를

만들 수 있도록 하고 있다. PLD 벤더들은 이것을 자사의 전략에 따라 서로 다른 이름으로 부르고

있지만, SoC 구현을 위한 최적의 솔루션을 제공한다는 데는 일치한다.

알테라는 이러한 솔루션을 SoPC (System on a Programmable Chip)로, 퀵로직은 ESP(Embedded Standard Products)라

부르고 있다. 한편, 자일링스는 IBM의 명령어축약형컴퓨팅(RISC) 방식의 PowerPC 프로세서 코어와 코어커넥트 버스를

라이선스하여 자사 버텍스(Virtex)-II FPGA에 내장시켰으며, 액텔은 임베디드 FPGA 디자인을 ASIC에 구현하는 색다른 전략을

구사하고 있다.

|

ALTERA |

Xilinx |

개요 |

알테라는 SOPC를 구현할 수 있는 Excalibur 임베디드

프로세서 솔루션과 IP 코어, 그리고 고집적화 된 디바이스 및

효과적인 툴 지원과 같은 분야에 알테라의 자본과 기술력을

집중하고 있다.

알테라의 SoPC는 PLD의 장점인 유연성과 SoC가 가지는

시스템 통합의 장점을 결합하여 사용자가 설계하고자 하는

로직은 PLD 영역에 기존과 동일한 공정에 따라 구현하고,

구현된 로직과 시스템과의 인터페이스 및 시스템의 설정 등은

툴 상에서 사용자 요구대로 선택만 하면 빠른 시간 내에

하나의 시스템을 설계할 수 있다.

뿐만 아니라, SoPC에서는 H/W적인 문제 못지 않게 S/W에

대한 비중도 높아지게 되는데 시스템에 동반되는 내부

프로세서들로 인하여 시스템 운영에 필요한 운영체제(OS),

그리고 전체 기능(function)의 일부분을 소프트웨어로 구현할

경우 등을 포함하여 S/W 개발에 필요한 툴 및 환경을

제공하게 된다. |

Xilinx사는 IBM의 PowerPC 프로세서와 3.125 Gbps로

동작하는 시리얼 I/O 트랜시버를 내장한 최초의 FPGA,

Virtex-II Pro를 출시했다. 최고 네 개의 PowerPC와 16개의

트랜시버를 하나의 다이에 통합시킨 Virtex-II Pro는 Virtex

라인을 발표한 이래 가장 중요한 FPGA 제품이라고 Xilinx사는

밝혔다

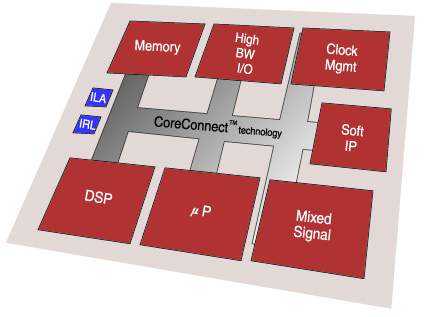

자일링스 플랫폼의 핵심은 Virtex-Ⅱ 플랫폼에 있는 IBM의

PowerPC 프로세서 코어와 같은 임베디드 프로세서이다.

전형적인 플랫폼은 버스, DSP, I/O 채널, 다양한 신호처리

기능, 메모리 및 구성 가능한(Configurable) 로직을 포함하고

있다 |

형태 |

|

|

내용 |

■ Nios

Nios는 알테라가 개발한 소프트코어 RISC 프로세서이다.

이 프로세서는 설계자가 툴에서 지정한 spec에 맞는 RISC

코어 및 주변 블록들의 HDL code가 자동적으로 생성되고

로직 synthesis 과정을 거쳐 Quartus에서 선택한

디바이스에 fitting을 마치면 최종적으로 디바이스를

프로그래밍하는 binary data를 이용하여 실질적인 시스템

회로를 PLD에 구현하게 된다.

따라서, PLD 영역에 적용시켜 프로세서를 포함한 각종

주변의 인터페이스 블록을 구현할 수 있다. 약 50MIPS

정도의 연산능력을 가지고 있으며 소프트코어이므로 향후

다양한 알테라 디바이스에 적용 가능한 장점을 가지고 있다.

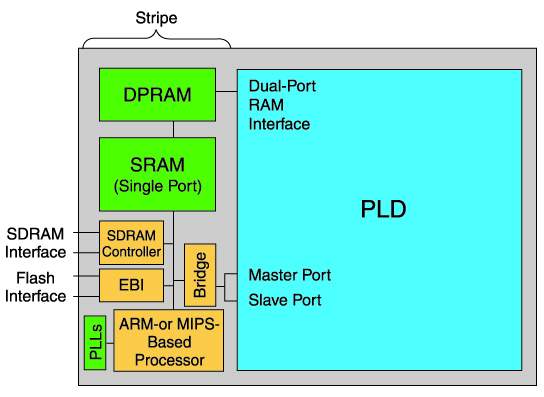

■ ARM

ARM사로부터 32비트 RISC 아키텍처인

ARM9TDMI(ARM922T) 코어를 라이선스하여 기존의 PLD

영역 이외의 스트라이프(stripe)라고 부르는 실리콘 상의

특정 영역에 ARM 코어, AHB 버스(ARM High performance

Bus로 AMBA 제품군 중 최근에 발표된 버스로 성능향상을

위하여 모든 동작을 클록 rising에 동기되도록 설계되어

있다), 내부 메모리 및 UART, 외부 메모리 컨트롤러 등을

집적했다.

Nios와는 달리 하드코어(Hardcore) 프로세서가

내장되어 있고, ARM9의 경우 ARM7에 비하여 코어 자체에

각각 8Kbyte의 데이터와 명령 캐시(instruction cache)를

가지고 있으며 200MHz에서 동작하도록 설계되어 있어

200MIPS 정도의 연산 성능을 가지고 있다.

■ MIPS

ARM 코어가 MIPS사의 MIPS32 4Kc 코어로 바뀐 디바이스로

스트라이프 영역의 나머지 부분이나 PLD 부분은 ARM과

동일하다. MIPS 코어는 ARM9 코어보다 많은 캐시 메모리를

포함하고 있으며(16Kbyte), 연산능력은 클록 한 주기 동안에

32bit×16bit MAC(곱셈과 덧셈을 동시에 수행하는 연산)을

수행한다. 또한 S/W 디버깅 시에 외부 디버그 툴과 서로

인터페이스 할 목적으로 EJTAG라는 내장 모듈을 포함하고

있다. |

자일링스는 IBM의 하드코어 PowerPC 405

마이크로프로세서를 Virtex-II 아키텍처에 임베디드 하고

있으며 300MHz에서 동작하여 420 Dhrystone Mips 이상의

성능을 구현한다. PowerPC 405 코어는 6Gbyte peak 이상의

통신 대역폭을 제공한다.

Xilinx의 최신 FPGA는 개발자들이 내장 프로세서들, 고속

시리얼 트랜스시버들, 로직 셀들 그리고 메모리를 단일

디바이스속으로 결합할 수 있도록 한다. Virtex-II Pro

Platform FPGA라 불리는 부품은 최대 50k 로직 셀들, 3.8k

비트의 블록 RAM, 최대 16개의 3.125 기가비트/초 시리얼

트랜스시버들, 그리고 디바이스 당 최대 4 개의 300-MHz

PowerPC 405 프로세서 코어들을 갖는 다섯 개의 버전들로

공급될 것이다.

Virtex-II Pro은 프로세서와 로직을 분배해서 사용하고 있다.

즉 PowerPC와 FPGA가 서로 독립적으로 동작한다. 다수의

작은 작업을 할 경우에는 PowerPC에서 처리하고,

복잡하고도 양이 큰 작업은 FPGA에서 처리한다.

또 하나의 중요한 기술 성과로는 622 Mbps에서 3.125

Gbps까지 확장 가능한 I/O 트랜시버를 포함하고 있다는

것이다. RocketIO로 명명된 이 기술은 Conexant사의

SkyRail 기술에 기반을 둔 기가비트 시리얼 인터페이스로서

기가비트 이더넷, 10 기가비트 이더넷, 3GIO, SerialATA,

Infiniband, FibreChannel 과 같은 고성능 인터페이스 표준을

지원한다.

Xilinx사는 Virtex-II FPGAs의 대안으로 사용되어 제조 비용을

최대 80 퍼센트까지 줄여 주는 Virtex-II EasyPath FPGA

솔루션을 출시했다. Xilinx사는 EasyPath 솔루션이 Virtex-II

FPGA와 대등한 기능을 발휘하지만 여기에 걸리는 시간은

기타 솔루션의 1/5 수준에 불과하다고 설명했다. |

비용 |

|

버텍스-II Pro FPGA는 RocketI/O과 시스템 레벨에서 통합돼

있으며, 프로세서 기술을 사용함으로써 시스템 비용을 크게

절감할 수 있다. XC2VP4TM, XC2VP7TM, XC2VP20 TM

디바이스는 현재 생산되고 있으며, XC2VP2와 XC2VP50도

올해 중반에 생산될 예정이다. XC2VP4, XC2VP7,

XC2VP20가 2004년 대량 생산될 경우, 예상 가격은(25,000개

단위 구입시) 각각 120달러, 180달러, 525달러이다.

XC2V3000용 버텍스-II 이지패스 솔루션의 2004년

대량구매(1만5천개 이상 구입시) 가격은 200달러가 채 안될

전망이다 |

관련 |

|

*버텍스-II Pro FPGA

*PLD에서 PLS로의 전환, 새로운 첨단 시스템 아키텍처

*자일링스, 버텍스-II 이지패스 제품군 출시

*Xilinx, Virtex-II FPGA를 대체할 수 있는 솔루션 발표

*PowerPC 내장의 강력한 FPGA" Xilinx, Virtex-II Pro 발표 |

|